Empyrean's EDA Software

Analog/Mixed-signal IC Design

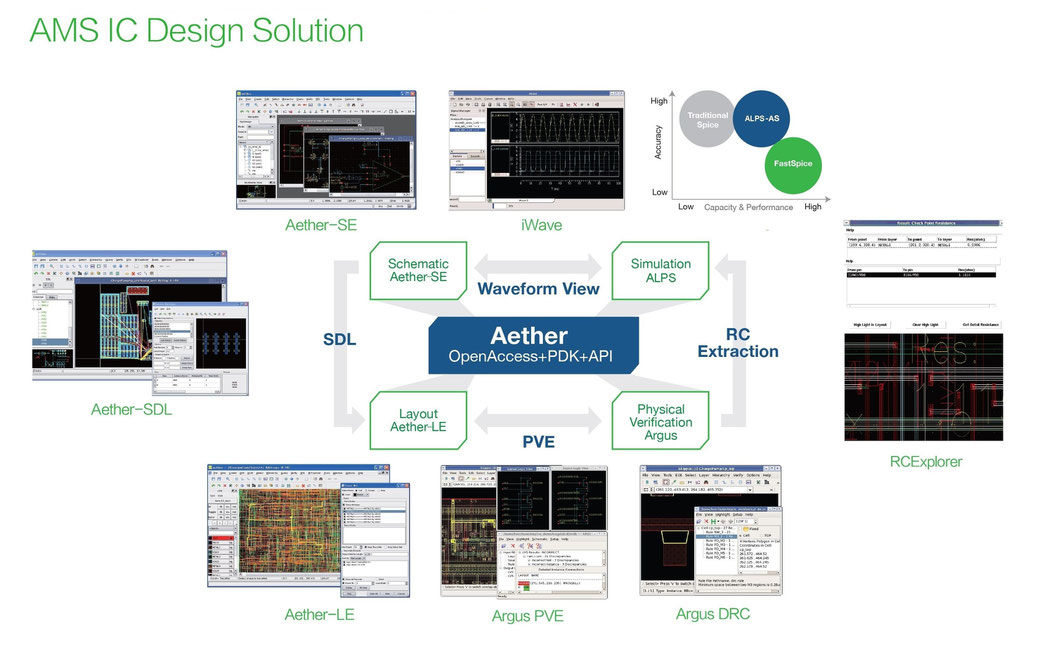

Empyrean offers a complete Analog and Mixed-Signal design solution with a competitive set of tools that covers schematic/layout (Aether), circuit simulation (ALPS), physical verification (Argus) and interconnect analysis (RCExplorer).

Empyrean’s Full-custom analog/mixed-signal IC design solution is based on OpenAccess standard data format; as well it supports the industry-standard iPDKs. As a total solution it integrates Empyrean’s Full-custom analog/mixed-signal IC design platform-Aether, high-performance SPICE simulator-Aeolus, waveform viewer-iWave, physical verification tool-Argus and 3D RC extraction tool-RCExplorer. It provides customers a smooth Full-custom analog/mixed-signal design flow with high efficiency, as well reduces design risks and time-to-market.

Video Demo:

Tools:

AETHER : Schematic and Layout Design Platform

Aether delivers a complete, integrated solution for custom IC designs using OpenAccess™ as the native database. This platform has several built-in modules such as design manager (Aether-DM), technology manager (Aether-TM), schematic editor (Aether-SE), layout editor (Aether-LE), schematic-driven layout (Aether-SDL), mixed-signal simulation environment (Aether-MDE), etc.

ALPS : Fast, High-Capacity Parallel SPICE Simulator

ALPS delivers SPICE-level accuracy with excellent performance and capacity for the most challenging analog and mixed-signal designs. This tool can simulate design with up to 10 million instances.

Compared to traditional SPICE tools, ALPS has significant performance speedup and gained additional speedup with its advanced parallel technique.On average, it can provide an additional four to seven times higher speedup in parallel simulation mode with eight threads by utilizing advanced multi-threading algorithm.

PVE : Layout verification

PVE is a graphical debugging environment for physical design tools. It allows you to browse and debug verification results after DRC and LVS runs. It probes DRC and LVS database results and back- annotates to layout viewer, schematic viewer, SPICE netlist browser and logic viewer. It is a powerful tool for users to easily debug DRC errors and LVS discrepancies.

ARGUS : Physical verification

Argus is a hierarchical and parallel physical verification tool that meets the requirements of ultra deep submicron IC designs. It effectively locates the design violations, reduces verification time and improves productivity. By integrating with full-custom IC design platform Aether and chip-finishing layout platform Skipper, Argus provides designers with an end-to-end physical verification solution.

RCEXPLORER : RC EXTRACTION

RCExplorer is an on-chip interconnect parasitic extraction and analysis tool for Analog, AMS and Digitial designs. RCExplorer generates distributed 3D capacitance and resistance including advanced manufacturing effects associated with 45nm processes and below. RCExplorer also provides easy-of-use functionalities for interconnect analysis after extraction. RCExplorer is intergrated with leading layout tools for both batch-mode and interactive usage

iWAVE : WAVE VIEWER

iWave is analog and mixed-signal waveform viewer and analyzer.

Contact Us:

Ambition Technologies

17-FF, Pocket 2, Sector 24

Rohini, New Delhi - 110085 India

Phone:

# 9810400671 / Pranay@ambitec.org

# 9911223020 / Rahul@ambitec.org

Email: sales@ambitec.org